Product Summary

The 74LS240 is an octal buffer and line driver designed specifically to improve both the performance and density of three-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. The designer has a choice of selected combinations of inverting and noninverting outputs, symmetrical, active-low output-control (G) inputs, and complementary output-control (G and G) inputs. The 74LS240 features high fan-out, improved fan-in, and 400-mV noise margin. The 74LS240 can be used to drive terminated lines down to 133Ω.

Parametrics

74LS240 absolute maximum ratings: (1)Supply voltage, VCC: 7 V; (2)Input voltage, VI: 7 V; (3)Off-state output voltage: 5.5 V; (4)Package thermal impedance, θJA: DB package 70℃/W; DW package 58℃/W; N package 69℃/W; NS package 60℃/W; (5)Storage temperature range, Tstg: -65℃ to 150℃.

Features

74LS240 features: (1)3-State Outputs Drive Bus Lines or Buffer Memory Address Registers; (2)PNP Inputs Reduce DC Loading; (3)Hysteresis at Inputs Improves Noise Margins.

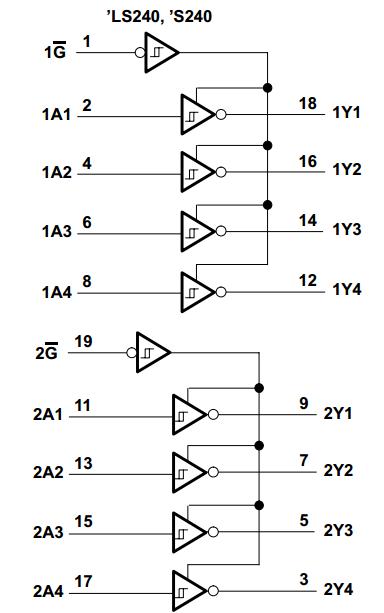

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

74LS240 |

Other |

|

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

74LS00 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74LS00N |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74LS01 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74LS03 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74LS05 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74LS08 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))